Article

Concentrator Integrated Chip

CIC : une première version fonctionnelle pour le futur agrégateur de données de CMS

Introduction

CMS est une des 4 expériences installées auprès du LHC au CERN. Ce détecteur est à l’origine, avec ATLAS, de la découverte du boson de Higgs en 2012. Le but principal de ces expériences est désormais de détecter de nouveaux phénomènes inexplicables via le Modèle Standard, qui ne permet de modéliser les interactions que jusqu’à un certain niveau d’énergie. C’est cette énergie que l’on espère atteindre au LHC.

D’ici à la fin de l’année 2023, une quantité de données correspondant à une luminosité intégrée de 300 fb‑1 aura été enregistrée avec la configuration actuelle du LHC. A ce stade, certains détecteurs et aimants soumis à des doses de radiations importantes seront en fin de vie. Un programme d’adaptation du collisionneur et des détecteurs est donc nécessaire pour aller au-delà et envisager de collecter encore 10 fois plus de données de collisions: c’est le programme HL-LHC. Ce projet, dont le démarrage est prévu en 2026, vise une collecte d’au moins 3000 fb‑1 sur une période de 10 ans.

Le futur trajectographe de CMS devra répondre aux défis complexes du HL-LHC. Pour ce faire, il sera plus précis que le détecteur actuel (meilleure granularité, moins de matière traversée), et ses données seront utilisées dès le premier niveau du système de déclenchement, à la fréquence de 40MHz. more detailed information regarding spin and win real. Alors que dans le détecteur actuel elles ne sont extraites qu’à partir du niveau 2 (HLT), à la fréquence de 100kHz.

Cette nouvelle contrainte est fondamentale, car elle induit une refonte totale de la chaîne d’acquisition, mais également du fonctionnement des modules de détection.

Description de la chaîne de détection

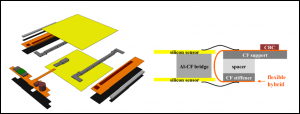

Le futur module de détection, nommé pT-module, est un élément clé du système. La figure 1 ci-après décrit un des 2 types de pT-modules qui seront installés dans le détecteur: les modules 2S (pour strips/strips). Les zones les plus internes seront équipées de module PS (pixels/strips), de granularité plus importante.

Figure 1 : Vue éclatée d’un pT-module

La structure de base, deux couches de détection en silicium (en jaune sur la figure) séparées de quelques mm, est un principe relativement standard dans les détecteurs de traces actuels. L’électronique de lecture, par contre, est entièrement nouvelle. En effet, comme on peut le voir sur la figure de droite, le signal des 2 couches peut être mis en coïncidence dans le module lui-même.

Ce point est fondamental, car il est ainsi possible de réduire significativement la quantité de signal à extraire (en pratique environ un ordre de grandeur). Cette première étape n’étant cependant pas suffisante, un second étage de compression est nécessaire pour parvenir à un niveau de données acceptable (quelques dizaines de Tb/s pour l’ensemble du détecteur, soit environ 15000 pT-modules).

Ce second étage est réalisé par le Concentrator Integrated Chip (CIC). Le CIC est un ASIC (Application-Specific Integrated Circuit) dont le développement est sous la responsabilité de l’IP2I depuis 2012. C’est un système complexe qui doit être compatible avec les différents types de modules de détection (selon la position du module dans le détecteur, 2 électroniques de lectures différente sont prévues) et résistant aux radiations. C’est également un point-clé de la chaîne d’acquisition, et notre engagement est de ce fait une responsabilité très importante.

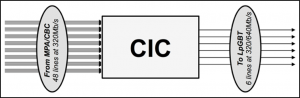

Figure 2 : Principe de fonctionnement du CIC

Le diagramme fonctionnel du CIC est schématisé sur la Figure 3 ci-après. Le circuit intégré reçoit les informations provenant de 8 ASICs identiques dans lesquels le signal a été préalablement numérisé et traité, il reformate ces données, les traite, et les groupe en paquets avant de les envoyer vers un autre ASIC qui effectue la transmission du signal en dehors du détecteur. Chaque pT-module contiendra 2 CICs, il y aura donc environ 30000 CICs dans le futur trajectographe.

Figure 3 : Diagramme bloc du CIC

Les caractéristiques du CIC sont résumées dans la table suivante :

| Technologie | CMOS 65nm à 7 niveaux de métal |

| Entrées | 48 voies différentielles à 320Mbps |

| Sorties | 7 voies différentielles at 320/640MHz |

| Alimentation I/Os | 1.2V |

| Alimentation cœur | 1V (PS) ou 1.2V (2S) |

| Consommation nominale (en mW) | 250 (PS) et 310 (2S) |

| Connectivité | Puce nue avec billes (Flip chip) |

Table 1 : Caractéristiques du CIC

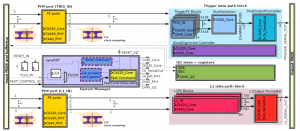

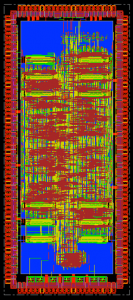

Figure 4 : Floorplan de l’implémentation physique du CIC1

Prototype du CIC et banc de tests

Afin de valider le modèle du CIC dans une chaine d’acquisition, une première version a été développée et mise en œuvre par une équipe du service électronique de l’IP2I. Le CIC1 contient l’ensemble des fonctionnalités du chip final et possède la même empreinte pour le câblage sur carte. La principale différence est que les techniques de résistance aux radiations n’ont pas été utilisées pour son design, alors que ce sera le cas pour la version finale.

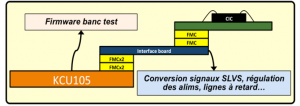

Figure 5 : Banc de test CIC1

Figure 6 : Banc de test

Figure 7 : Mezzanine CIC1

Les premiers échantillons du CIC1 sont arrivés à l’IP2I en Janvier 2019, ils ont pu alors être très rapidement testés grâce à un système développé également à l’IP2I

Ce système de test a permis de vérifier le bon fonctionnement de l’ASIC : le traitement des données reçues correspond au cahier des charges. Les premières mesures de puissance correspondent aux estimations et ouvrent la voie à une caractérisation en puissance de l’architecture, très importante au vu des contraintes du trajectographe.

Conclusions et perspectives

Les résultats observés jusqu’à présent sont très encourageants pour la suite : la prochaine étape du projet est la réalisation d’ici la fin de l’année 2019 d’une version de pré-production de l’ASIC, le CIC2. Ce chip sera résistant aux radiations et il inclura des modifications permettant de réduire la consommation nominale. La production finale des 30000 CIC qui seront installés dans le futur trajectographe est prévue pour 2020.

Un grand nombre de personnes, appartenant à l’IP2I, au CERN et à d’autres instituts dans la collaboration CMS, ont contribué à ce projet depuis son démarrage en 2012. Les personnes suivantes ont contribué de manière significative au succès du projet à l’IP2I, sous la responsabilité scientifique de Sébastien Viret:

- ASIC : Luigi Caponetto (resp. technique), Geoffrey Galbit, Benedetta Nodari

- Banc de test : Cyrille Guérin, William Tromeur

Contacts : Sébastien Viret et Luigi Caponetto