Article

Circuit Intégré Cryogénique QUBIC :

Conception à 4 Kelvin

Depuis une dizaine d’années le laboratoire APC développe une expertise spécifique au sein de l’IN2P3 dans le domaine de la conception de circuits intégrés (ASIC : Application Specific Integrated Circuit) ultra-bas-bruit (0,2 nV/√Hz), opérant en milieu cryogénique (4,2 K) pour l’intégration de senseurs supraconducteurs.

Contexte du projet QUBIC

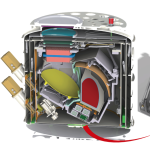

La réalisation de l’ASIC “SQMUX128” s’inscrit dans le cadre du projet de cosmologie observationnelle QUBIC. Le détecteur de QUBIC s’appuie sur le nouveau concept instrumental qu’est l’interférométrie bolométrique. Son architecture met en œuvre 2 plans focaux de 1024 détecteurs bolométriques chacun (voir article déjà publié sur ce sujet). Ces détecteurs sont refroidis à une centaine de mK. Chaque plan focal est subdivisé en 8 blocs de 128 détecteurs bolométriques associés à une électronique de lecture et de multiplexage temporel (TDM), elle-même constituée de 128 SQUID et d’un ASIC fonctionnant à température cryogénique (60 – 70 K). Un module complet de l’instrument QUBIC est composé de 16 ASIC (voir image ci-dessous).

ASIC “SQMUX128”

L’amélioration de la sensibilité des instruments pour l’étude du fond diffus cosmologique (CMB) nécessite le développement de plans focaux disposant d’un nombre toujours plus important de pixels. Avec ses deux plans focaux de 1024 bolomètres, l’instrument QUBIC ne déroge pas à cette tendance. Une stratégie de multiplexage doit donc être mise en œuvre pour permettre de réduire le nombre de câbles associés à chacun de ces détecteurs TES (Transition-edge sensor) afin de minimiser la puissance cryogénique nécessaire pour leur refroidissement et garantir l’intégrité des signaux à traiter.

|

|

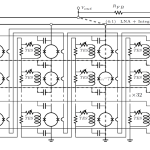

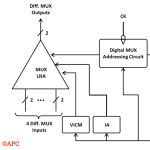

| Architecture du multiplexeur temporel constitué de 4 colonnes de 32 SQUID en série | Blocs fonctionnels implémentés dans l’ASIC “SQMUX128” |

l’ASIC “SQMUX128” réalise le multiplexage temporel de 4 colonnes de 32 SQUID en série pour la lecture de 128 TES. L’ASIC intègre :

- un amplificateur de tension ultra bas bruit à 4 entrées multiplexées pour la lecture des 4 colonnes de SQUID ;

- une source de courant pour la polarisation de l’amplificateur multiplexé ;

- une source de courant de polarisation AC associée à un multiplexeur 1:32 pour l’adressage des 32 lignes de SQUID au travers de capacités d’adressage ;

- deux références de tensions pour l’ajustement du mode commun en entrée de l’amplificateur multiplexé et en sortie de la source de polarisation AC des SQUID ;

- un circuit numérique qui, à partir d’un signal d’horloge externe (fMUX = 100 kHz), permet de gérer l’adressage ligne / colonne du multiplexeur ;

- un lien série pour l’adressage des blocs paramétrables comme les références de tension, les sources de courant de polarisation ou le circuit d’adressage ligne / colonne du multiplexeur.

Cet ASIC, réalisé en technologie standard BiCMOS SiGe 0,35 µm d’Austria MicroSystem (AMS), alimenté sous 3,3 V, affiche une consommation nominale de 16 mW (quel que soit le nombre de colonnes lues) et fonctionne à température cryogénique de 4,2 K.

|

|

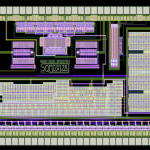

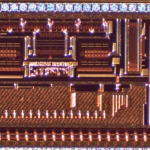

| Layout du circuit | Puce issue de la fonderie |

Conception à température Cryogénique

Le circuit SQMUX128 est basé sur une technologie commerciale standard BiCMOS SiGe 0,35 µm d’AMS (Austria Microsystem) garantissant un process stable et reproductif.

Cependant aux températures cryogéniques les modèles de simulations fournis par les fondeurs n’étant plus valides et faute de moyens et de temps nécessaires pour les développer, on est contraint de s’appuyer sur des résultats issus d’une phase de caractérisation expérimentale préalable de la technologie visée. Cette phase est nécessaire pour pré dimensionner les circuits et extrapoler leurs performances à température cryogénique en fonction des résultats de simulation obtenus, à température ambiante, à l’aide des outils de CAO standards (cette phase est détaillée ci-dessous).

Le choix d’une technologie commerciale standard garantit un process stable et une reproductibilité des performances d’un run à l’autre. Par ailleurs, les transistors bipolaires à hétérojonction Silicium Germanium (SiGe) et par voie de conséquence les technologies BiCMOS SiGe sont particulièrement prédisposées aux applications cryogéniques. En effet, les HBT (Heterojunction Bipolar Transistors) SiGe présentent, à basse température, des performances accrues notamment en termes de transconductance et de gain en courant ce qui rend leur utilisation propice aux développements de fonctions analogiques comme l’amplification de signaux. A contrario, les transistors MOS étant soumis au phénomène de kink‑effect pour des températures T ≤ 30 K, on réservera leur usage essentiellement à la réalisation des circuits numériques, moyennant des précautions d’usage au niveau layout pour s’affranchir des effets de gel des porteurs.

En contrepartie, les modèles de simulation fournis par les fondeurs n’étant plus valides pour des températures de fonctionnement cryogéniques et faute de moyens et de temps nécessaires pour les développer, on est contraint de s’appuyer sur des résultats issus d’une phase de caractérisation expérimentale préalable de la technologie visée. Cette phase est nécessaire pour pré dimensionner les circuits et extrapoler leurs performances à température cryogénique en fonction des résultats de simulation obtenus, à température ambiante, à l’aide des outils de CAO standards.

Cette méthodologie nous contraint le plus souvent à adopter des topologies de circuit simples et robustes dans le sens où il faut à coup sûr pouvoir prédire et anticiper les dérives éventuelles des principaux paramètres comme les points de fonctionnement, le gain, la bande passante, la marge de phase pour les systèmes contre‑réactionnés, etc…

Ainsi, à titre d’exemple, l’amplificateur bas‑bruit implémenté dans l’ASIC “SQMUX128” est constitué d’un étage différentiel à charges résistives (RL) pour lequel les points de fonctionnement et les performances sont déterminés sans ambiguïté à partir des résultats de caractérisation en température collectés préalablement.

L’expression du gain en tension différentiel est donnée par :

AVD » ‑gm×RL

Sachant que de 300 K à 4,2 K on bénéficie d’un accroissement d’un facteur 5 de la transconductance gm des transistors bipolaires pour la technologie considérée :

gm(T) = α(T)×IC/26 mV où 26 mV = VT = kT/q à T = 300 K

α(T) étant le paramètre d’ajustement en température, déterminé expérimentalement :

α(T = 300 K) » 1 et α(T = 4,2 K) » 5

L’ajustement de la valeur du gain consiste donc à déterminer IC et RL tout en prenant en compte l’évolution de α(T) pour un fonctionnement à une température T donnée.

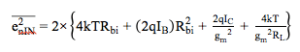

Par ailleurs, la DSP équivalente de bruit en tension, ramenée en entrée, dans la zone de bruit blanc est :

La contribution des deux premiers termes est minimisée en mettant un grand nombre de transistors constituant la paire différentielle en parallèle pour réduire la valeur de la résistance de base intrinsèque Rbi globale. L’optimisation des performances en bruit consiste alors à déterminer IC et RL pour minimiser la contribution prédominante des deux derniers termes. Un fonctionnement à basse température contribue intrinsèquement à une diminution du bruit blanc.

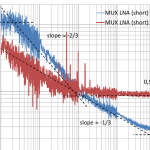

Une fois fondu et avant d’être intégré dans la chaîne de lecture de l’instrument pour lequel il a été développé, l’ASIC a été testé fonctionnellement et caractérisé qualitativement. Ainsi, concernant l’amplificateur bas‑bruit intégré, de 300 K à 77 K, le gain en tension mesuré passe de 20 V/V à 70 V/V et la tension de bruit blanc diminue de 0,95 nV/√Hz à 0,25 nV/√Hz.

|

Spectres de tension de bruit ramenés en entrée de l’amplificateur mesurés à 300 K et 77 K |

Validation de la chaine de détection

Les tests de validation de la chaîne de détection QUBIC ont été réalisés sur un sous‑ensemble correspondant à un quart de plan focal de l’instrument assemblé dans un cryostat à dilution de l’APC. L’ensemble du processus de validation est détaillé ci-dessous avec les principaux résultats.

La matrice de 256 TES, réalisée au CSNSM et à l’IEF d’Orsay, est refroidie à une température de 100 mK. L’électronique de lecture associée est constituée d’un premier étage à SQUID (préamplificateur transimpédance cryogénique ultra‑bas bruit). A chaque TES est associé un SQUID (puce de la compagnie américaine STARCryo), au total, 256 SQUID refroidis à une température de 1 K sont donc nécessaires pour la lecture d’un quart de plan focal. Les ASIC que nous développons permettent la mise en œuvre du multiplexage temporel de 128 SQUID. Les tests de validation ont donc été réalisés en utilisant 2 ASIC “SQMUX128” placés sur l’étage à 77 K de la dilution.

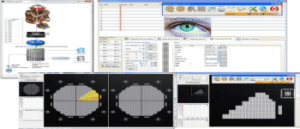

Le système d’acquisition et de contrôle à température ambiante (cartes “NetQuiC”), sous la responsabilité de l’IRAP (Toulouse), regroupe l’ensemble des fonctions nécessaires à la numérisation et au traitement du signal multiplexé ainsi que la génération des signaux utiles pour la gestion des circuits fonctionnant à température cryogénique. L’IRAP a également développé l’interface software (logiciel “QUBIC Studio”) pour le contrôle du multiplexeur, l’acquisition des données et leur visualisation.

Des tests fonctionnels préliminaires ont tout d’abord permis de valider l’architecture globale de la chaîne de lecture avec un taux de multiplexage temporel effectif jusque‑là jamais atteint de 1:128 par voie de mesure. Cette chaîne de lecture a été ensuite mise à contribution pour la caractérisation des matrices de TES.

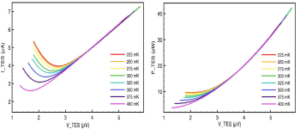

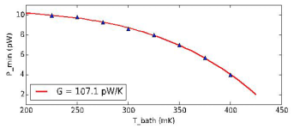

Les TES sont polarisés à tension constante pour bénéficier de la contre‑réaction électrothermique (Electrothermal Feedback ou ETF) et travailler à puissance minimale (Pmin) constante. Un relevé automatique des caractéristiques I‑V et P‑V est réalisé pour chaque TES à différentes températures de bain sous la TC (température critique). A partir de ces mesures, on reporte sur un graphe l’évolution de Pmin en fonction de la température de bain. Un ajustement de cette courbe permet alors d’extraire les paramètres, notamment la conductance thermique G, nécessaires à l’estimation du NEP (Noise Equivalent Power) de chaque TES.

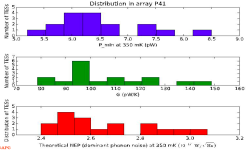

En reproduisant cet exercice sur une vingtaine de TES aléatoirement distribués sur une matrice de 256 pixels (P41) on obtient l’histogramme de Pmin de tous les pixels testés pour une température de bain de 350 mK. L’histogramme de G donne une valeur moyenne de 106 pW/K. On en déduit, en première approximation, la distribution du NEP avec une valeur moyenne de 2,6 ×10‑17 W/√Hz à 350 mK. Cette valeur est pleinement compatible avec les besoins de l’instruments QUBIC (NEP 5 ×10-17 W/√Hz).

|

|

| Intégration d’un quart de plan focal de l’instrument QUBIC | Interface du logiciel “QUBIC Studio” |

Mesures et résultats issus de cette validation

|

|

|

|

Depuis, d’autres matrices ont pu être testées avec succès à l’aide de cette même chaîne de lecture multiplexée en vue de stabiliser le procédé de fabrication des TES. Cette chaîne de lecture constitue à présent un outil de caractérisation et de sélection des matrices de bolomètres destinées à équiper le premier module de l’instrument QUBIC.

L’expertise acquise par l’APC dans la conception d’ASIC pour la mise en œuvre de multiplexeurs à SQUID pour le readout de grandes matrices de TES est reconnue internationalement. Le projet spatial ATHENA de l’ESA (European Space Agency) a retenu cette expertise pour le développement de l’ASIC de la chaîne de lecture WFEE de l’instrument X‑IFU